# THE WEENY-BITTER

# INTRODUCTION

The WEENY-BITTER is a simple 256 word, 8 bit machine which can be built for around £50, without peripherals, but which is capable of enhancement by the addition of more memory and some extra instructions. In the enhanced form (which can handle up to 64K bytes of memory) it is a fairly powerful mini; the basic machine can be used to play simple computer games, as an educational unit; a controller/sequencer for household devices, model train layouts; a sophisticated code converter, peripheral controller for a larger machine etc.

This first article describes the fundamental machine characteristics and instruction set. Future articles will describe the hardware of the basic machine (WB-1), programming techniques hardware enhancements to upgrade to the WB-2, and possibly various I/O devices.

# FUNDAMENTAL MACHINE CHARACTERISTICS

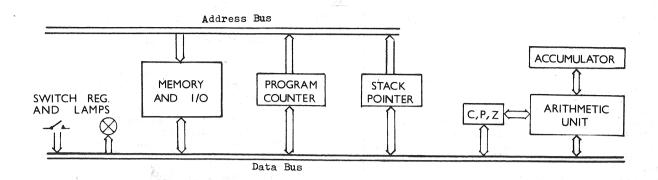

The block diagram above shows the major units of the Weeny-Bitter as it appears to the machine language programmer - the actual hardware configuration is somewhat different as will be explained in a subsequent article.

### Memory

This consists of a number of locations (256. for the WB-1, up to 65536. for the enhanced version) each capable of holding one eight bit word. The word may be either data or instructions, the memory does not differentiate between them. Each word in the memory has a unique address - thus the WB-1 has 256. locations numbered 0 to 255. (0 to 377 in octal). The low 4 words of memory are represented in the diagram below:

|               | ,    |

|---------------|------|

| octal address | word |

| 003           | 123  |

| 002           | 001  |

| 001           | 001  |

| 000           | 377  |

In this example, location 003 (binary 00000011) contains the eight bits 01010011 (octal 123), location 000 contains all 'ones' (octal 377), and locations 001 and 002 both contain octal 001.

The contents of specified locations may be modified, read out or replaced by new words. Certain memory locations are reserved for special uses; these are detailed later.

#### Program Counter

This is a register which contains the address of the next instruction word in memory. It is automatically incremented by one as each instruction word is read from memory and the contents may be changed to jump to another part of the program.

#### Stack Pointer

This register is not equipped on the basic WB-1. It contains the address of the top word of the stack (in memory). When a word is 'pushed' onto the stack the contents of the stack pointer are incremented by one and are then used to define the memory location into which the data word is stored.

Data is 'popped' from the stack by reading it from the location defined by the Stack Pointer after which the contents of the Stack Pointer are decremented by one. For example, if the SP contains the address 100, pushing a data word A onto the stack will cause A to be stored at location 101 and the SP contents changed to 101. A subsequent push of data word B will store it in location 102 and change the SP to 102. Popping will then get word B and change the SP back to 101. The stack is mainly used to store the return address for subroutine and interrupt calls.

#### Accumulator

This is an eight bit register used to hold one of the operands in certain operations.

# Arithmetic Unit

This unit performs the arithmetic/logical operations involved in instructions such as ADD, INC, AND.

C, P,& Z

These are one bit registers used in conjunction with the arithmetic unit. Their functions are;

C holds the carry bit resulting from an addit-

ion, subtraction or shift operation.

P holds the inverse of the most significant bit of the result of the latest operation. When data is treated as a two's complement signed binary number this bit is the sign bit (one for negative) therefore P is one for positive, zero for neg. Z is set to one if the result of the last

operation (ignoring the C bit) was all zeroes. If not it is cleared to zero.

### Input / Output

There are no special Input/Output instructions, but all I/O ports are made to look like memory

locations and are thus handled with the standard memory reference instructions. The address chosen for an I/O port may be the same as one of the existing memory locations, in this case the memory is inhibited during operations involving that narticular address.

tch Register

Eight switches form a primitive input port and allow the user to enter instructions and data into the machine.

Eight lamps can be used as a primitive output port to allow the user to examine the contents of memory locations and various registers.

#### OCTAL . DECIMAL & BINARY

One difficulty that appeared when people first started to use binary computers was that of representing the binary data as used by the machine in a way that mere humans can easily use - a string of binary digits e.g. 1001101100010 is not easily remembered. Translation into decimal gives a number (4962 in this case) which can be handled easily by humans but the translation between binary and decimal is tedious and rather error prone. To overcome these difficulties the Octal number system is now used almost universally to represent binary numbers.

Octal is a number system to the base 8, using the digits 0 to 7 inclusive, so you count;

0, 1, 2, 3, 4, 5, 6, 7, 10, 11, . . .

17, 20, 21, . . 77, 100, 101 .

The big advantage is that each octal digit is

exactly equivalent to 3 binary digits;

| 0 | == | 000 |  |  | 4 | = | 100 |

|---|----|-----|--|--|---|---|-----|

| 1 | =  | 001 |  |  | 5 | = | 101 |

| 2 | =  | 010 |  |  | 6 | = | 110 |

| 3 | =  | 011 |  |  | 7 | = | 111 |

The binary number is converted to octal by dividing it into groups of 3 bits, starting at the right (least significant) end, and translating each group of 3 bits into an octal digit, for example the binary bumber given above is broken down into

1, 001, 101, 100, 010

which gives octal

1 - 1

Thus the 8 bit word used in the WB divides into three groups; XX, XXX, XXX and can therefore be represented by a three digit octal number in the range 000 to 377.

To avoid confusion, all decimal numbers in this article are written with a decimal point (eg 255.) to distinguish tham from octal numbers unless the number is obviously decimal i.e. it contains one of the digits 8 or 9 which are not valid in octal.

#### OCTAL-DECIMAL-BINARY CONVERSION TABLE

| Octal | Decimal | Binary   | Decimal | Octal | Binary   |

|-------|---------|----------|---------|-------|----------|

| 10    | 8.      | 1000     | 10.     | 12    | 1010     |

| 20    | 16.     | 10000    | 20.     | 24    | 10100    |

| 30    | 24.     | 11000    | 30.     | 36    | 11110    |

| 40    | 32.     | 100000   | 40.     | 50    | 101000   |

| 50    | 40.     | 101000   | 50.     | 62    | 110010   |

| 60    | 48.     | 110000   | 60.     | 74    | 111100   |

| 70    | 56.     | 111000   | 70.     | 106   | 1000110  |

| 100   | 64.     | 1000000  | 80.     | 120   | 1010000  |

| 200   | 120.    | 10000000 | 90.     | 132   | 1011010  |

| 300   | 192.    | 11000000 | 100.    | 144   | 1100100  |

| 400   | 256. 1  | 00000000 | 200.    | 310   | 11001000 |

|       |         |          |         |       |          |

#### INSTRUCTION SET

There are four basic classes of machine language instruction .:

- Two operand e.g. A plus B

- One operand e.g. Increment A

- Program control e.g. Go to

- Miscellaneous e.g. Halt

Although the instructions are basically binary (or octal) words, mnemonic equivalents are given for ease of use.

#### Two Operand Instructions

These are of the general form OP P Q where the OPeration is performed between two data words P and Q and the result then replaces Q, P remaining unchanged.

P may be;

- the content of the Accumulator (A)

- data in the word immediately following the instruction word (D)

- data in memory location X where X is derived from the second word of the instruction according to the 'mode' bits (see section on addressing modes)

Q may be;

mnemonic

- the content of the Accumulator (A) - data in memory location X where X is derived from the second or third word of the instruction.

The allowable forms are;

| OP | #D | A | 11R | DDD |     | Acc | := | Acc | OP | data | DDD |

|----|----|---|-----|-----|-----|-----|----|-----|----|------|-----|

| OP | Х  | A | n2R | XXX |     | Acc | := | Acc | OP | mem  | :   |

| OP | #D | X | n5R | DDD | XXX | mem | := | mem | OP | data | DDD |

| OP | A  | X | n6R | XXX |     | mem | := | mem | OP | Acc  |     |

where n defines the addressing mode and R the operation. For example, using the SUBtract operation with addressing mode O (direct , first 256 words) we can have:

| SUB #D A | 112 222 subtracts     | octal 222 from |

|----------|-----------------------|----------------|

|          | the Acc.              |                |

| SUB X A  | 022 222 subtracts     | the contents   |

|          | of memory             | location 222   |

|          | from the              | Acc.           |

| SUB #D X | 052 222 333 Subtracts | octal 222 from |

|          | memory lo             | cation 333     |

| SUB A X  | 062 222 Subtracts     | the contents   |

|          | of the Ac             | c from memory  |

|          | location              | 222            |

### Operations

| MOV T Q | Q is replaced by T, T remains unchanged.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (**0)   | C becomes zero, P & Z set to one or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | zero depending on T.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| m -     | The state of the s |

| ADD T Q | T is added to Q, T remaining unchanged. |

|---------|-----------------------------------------|

| (**1)   | Result put in Q. C, P & Z set to one    |

|         | or zero depending on the result.        |

| SUB T Q | T is subtracted from Q, result in Q, T |

|---------|----------------------------------------|

| (**2)   | remains unchanged. C, P & Z set to one |

|         | or zero depending upon result.         |

| AND T Q | Q is replaced by the logical AND of T   |

|---------|-----------------------------------------|

| (**3) · | and Q. T remains unchanged. C is set to |

|         | zero, P & Z set to one or zero depend-  |

|         | ing on result.                          |

|       | Q is replaced by the logical inclusive |

|-------|----------------------------------------|

| (**4) | OR of Q & T. T remains unchanged. C is |

|       | set to zero. P & Z set to one or zero  |

|       | depending upon result.                 |

| XOR T Q | Q is replaced b | by the lo | ogical | exclusive |

|---------|-----------------|-----------|--------|-----------|

| (**5)   | OR of Q & T. T  |           |        |           |

|         | set to zero. P  | & Z set   | to one | e or zero |

|         | depending upon  | result    |        |           |

|         |      |      |     | -   |      |       |       |        |       |

|---------|------|------|-----|-----|------|-------|-------|--------|-------|

| BIT T Q | As X | OR I | ે Q | exc | ept  | that  | the   | result | is    |

| (**6)   | not  | put  | in  | Q,  | whic | h rem | nains | unchar | iged. |

|         |      |      |     |     |      |       |       |        |       |

| CMP T Q | AS SUB T Q | except that  | the result is   |

|---------|------------|--------------|-----------------|

| (**7)   | not put in | Q, which rem | ains unchanged. |

#### One Operand Instructions

These are of the general form OP Q where the OPeration is performed on the single data word Q.

Q may be:

- the content of the Accumulator (A) - data in memory location X where X is derived from the second word of the instruction.

The allowable forms are;

mnemonic octal

OP A Acc := Acc OP OP X n4R XXX mem := mem OP where n defines the addressing mode and R the operation. For example, using the INCrement operation with addressing mode O (direct, first 256 words) we can have;

INC A 101

Increments the Accumulator

INC X 041 222

Increments the contents of memory location 222

#### Operations

CLA Q Clear Q to zero. C is set to zero, P and Z (\*\*0)are set to one.

INC Q Increment Q by one. C, P & Z are set to

(\*\*1) one or zero depending on result.

Decrement Q by one. C, P & Z are set to DEC Q

one or zero depending on result. (\*\*2)

ADC Q Add C bit to Q.C. P & Z are set to one or

zero depending upon result. (\*\*3)°

TST Q Q is examined and P & Z set accordingly.

Q remains unchanged. C set to zero (\*\*4)

Invert all bits in Q. C set to zero, P  $\&~\mathrm{Z}$  set to one or zero depending on result. INV Q

(\*\*5)

Shift Q right one place, most significant SHR Q

bit  $(B_I)$  becomes 0, least significant bit (BO) shifted into C. P set to one. Z set (\*\*6)to one or zero depending on result.

SHL Q Shift Q left one place. Most significant bit (B7) shifted into C, BO becomes O. (\*\*7)P & Z set to one or zero according to result.

# Program Control Instructions

The GO TO and JMS instructions control the flow of the program, either unconditionally or according to the state of the C, P & Z bits. They are both 2 word instructions of the form

where X (with the memory address mode bits) defines the memory location to which the program is to go. e.g. using the unconditional GO TO and mode O (direct, first 256 words) we can have;

which causes the program to go to location 222 by loading GTO X 030 222 this number into the Program Counter.

The JMS instruction (not implemented in the basic machine) puts the program counter contents, which are the address of the instruction after the JMS instruction, onto the stack before loading the Program Counter with the new value. The GTO instruction loses the old value of the Program Counter.

#### Miscellaneous Instructions

These are all single word instructions;

HLT (000) stops program execution

NOP (001) is a 'filler', the machine accepts it but does nothing before passing to the next instruction.

CLC and SEC (002 & 003) are used to set and clear the C bit

ION and IOF (004 & 005) are not implemented on the basic machine

RTS and RTI (006 & 007) , not implemented in the basic machine, return program control from a subroutine or interrupt by loading the program counter with the address previously stored on the stack by the JMS instruction or by the interrupt.

### RESERVED MEMORY LOCATIONS

Certain memory locations are reserved for special functions;

| address      | function                      |  |  |  |  |

|--------------|-------------------------------|--|--|--|--|

| 000          | Accumulator 300 000           |  |  |  |  |

| 001          | Switch Register               |  |  |  |  |

| 002          | Low 8 bits of Program Counter |  |  |  |  |

| <b>+0</b> 03 | High" " " " "                 |  |  |  |  |

| +004         | Low 8 bits of Stack Pointer   |  |  |  |  |

| +005         | High " " " " "                |  |  |  |  |

+not used in the basic machine

Locations 007 to 037 should also be reserved, for use by I/O ports

### MEMORY ADDRESSING MODES

The eight address bits (X) assosciated with memory reference instructions of the form:

> OP X A OP #D X OP A X GTO/JMS X

are interpreted according to the 'mode' bits of the instruction (B7 & B6) as follows;

mode B7 B6

0 0 O Direct. The number X is the required address (one of the first 256 words)

Indirect. The required address is located in memory locations X and X+1 (low 8 bits in X, high 8 bits in X+1)

Relative. The required address is 1 obtained by adding (X-200) to the current contents of the Program Counter.

1 Indirect Relative. 1

Only mode O is implemented in the basic WB-1. Note that the indirect modes (1&3) generate a 2 word (16 bit) address, allowing the enhanced machine to use up to 64K bytes of memory.

#### BINARY ARITHMETIC

#### Addition

This is done according to the rules;

0 + 0 = 01 + 0 = 11 + 1 = 10 (0, carry 1)

Thus:

00 000 101 00\_000 110 (6) 00 001 011 (11.)

Any carry resulting form the most significant bit position is put into the C register;

, C=0 11 111 110 + 00 000 001 = 11 111 111 11 111 110 + 00 000 010 = 00 000 000 11 111 110 + 00 000 011 = 00 000 001 , C=1

#### Subtraction

Is done according to the rules;

0 - 0 = 01 - 0 = 11 - 1 = 00 - 1 = 1 , borrow 1

```

Any 'borrow' resulting from the most signific-

ant bit position is put into the C register;

00 000 100 - 00 000 001 = 00 000 011 ,C=0

00 000 100 - 00 000 100 = 00 000 000

00 000 100 - 00 000 101 = 11 111 111

Note that the last example (4 - 5) gives a negative answer (-1) which is represented in binary form as 11 111 111 . This is known as the 'Twos Complement' form which is the way the WB

represents negative numbers.

The Twos Complement of a number is defined as

that number which when added to the original num-

ber will result in a sum of zero (ignoring the

carry out to the C reg). Thus the positive number

00 000 001 has a twos complement equal to

11 111 111 as shown by the following addition

00 000 001

+ 11 111 111

1 00 000 000

The easiest way to generate a twos complement is

to first invert each bit then add one to the

00 000 010 number

11 111 101

inverted

11 111 110 twos complement

In Twos Complement form all negative numbers

have the most significant bit (B7) equal to one,

while all positive numbers have it equal to zero.

The range of numbers which can be expressed by a

eight bit word is;

11 111 111

11 111 110

(-2)

10 000 000

(-128.)

01 111 111

(+127.)

00 000 001

(+1)

00 000 000

(0)

BINARY LOGIC

AND

is performed according to the rules;

O AND O = O

0 \text{ AND } 1 = 0

1 \text{ AND } 0 = 0

1 \text{ AND } 1 = 1

thus:

11 000 111

AND 10 100 011

10 000 011

Inclusive OR

the IOR function is performed as;

0 IOR O = 0

0 IOR l = 1

1 IOR 0 = 1

1 IOR 1 = 1

thus;

11 000 111

10 100 011

TOR

11 100 111

Exclusive OR

the XOR function is performed as;

```

O XOR O = O0 XOR 1 = 11 XOR O = 1

$1 \times 0 \times 1 = 0$

thus;

11 000 111 XOR 10 100 011 01 100 100

AMATEUR COMPUTER CLUB NEWSLETTER Vol 3 Iss 3 August 175

Complete list of WEENY-BITTER instructions

| Comple                                                             | te list of WEE                                                                       | NY-BITTER instructions                                                                                                                                                                             |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic symbol                                                    | Octal<br>code                                                                        | Operation                                                                                                                                                                                          |

| HLT<br>NOP<br>CLC<br>SEC<br>+ION<br>+IOF<br>+RTS<br>+RTI           | 000<br>001<br>002<br>003<br>004<br>005<br>006<br>007                                 | Halt, stops program No Operation Clear C bit to zero Set C bit to one Interrupt enable on Interrupt enable off Return from subroutine Return from interrupt                                        |

| CLA A INC A DEC A ADC A TST A INV A SHR A SHL A                    | 100<br>101<br>102<br>103<br>104<br>105<br>106<br>107                                 | Clear Acc Increment Acc Decrement Acc Add C bit to Acc Test Acc Invert all bits of Acc Shift Acc right one place Shift Acc left one place                                                          |

| SUB #D A                                                           | 111 DDD<br>112 DDD<br>113 DDD<br>114 DDD<br>115 DDD<br>116 DDD                       | Move data D to Acc Add data D to Acc Subtract data D from Acc And data D with Acc Inclusive OR D with Acc Exclusive OR D with Acc Bit Test data D with Acc Compare data D with Acc                 |

| AND X A<br>IOR X A                                                 | n20 XXX<br>n21 XXX<br>n22 XXX<br>n23 XXX<br>n24 XXX<br>n25 XXX<br>n26 XXX<br>n27 XXX | Move mem X to Acc Add mem X to Acc Subtract mem X from Acc And mem X with Acc Inclusive OR mem X with Acc Exclusive OR mem X with Acc Bit Test mem X with Acc Compare mem X with Acc               |

| GTO X GIZ X GNZ X GPL X GMI X GCS X GCC X                          | n30 XXX<br>n32 XXX<br>n33 XXX<br>n34 XXX<br>n35 XXX<br>n36 XXX                       | Go to X Go to X if zero (Z=1) " " " " not zero (Z=0) " " " " positive (P=1) " " " negative (P=0) " " " C bit set (C=1) " " " C bit clear (C=0)                                                     |

| CLA X INC X DEC X ADC X TST X INV X SHR X SHL X                    | n40 XXX<br>n41 XXX<br>n42 XXX<br>n43 XXX<br>n44 XXX<br>n45 XXX<br>n46 XXX<br>n47 XXX | Clear mem X Increment mem X Decrement mem X Add C bit to mem X Test mem X Invert all bits of mem X Shift mem X right one place Shift mem X left one place                                          |

| ADD #D X SUB #D X AND #D X IOR #D X XOR #D X BIT #D X              | n53 DDD XXX<br>n54 DDD XXX<br>n55 DDD XXX                                            | Move data D to mem X Add data D to mem X Subtract data D from mem X And data D with mem X Inclusive OR D with mem X Exclusive OR D with mem X Bit Test data D with mem X Compare data D with mem X |

| MOV A X ADD A X SUB A X AND A X IOR A X XOR A X BIT A X            | n60 XXX<br>n61 XXX<br>n62 XXX<br>n63 XXX<br>n64 XXX<br>n65 XXX<br>n66 XXX            | Move Acc to mem X Add Acc to mem X Subtract Acc from mem X And Acc with mem X Inclusive OR Acc with mem X Exclusive OR Acc with mem X Bit Test Acc with mem X Compare Acc with mem X               |

| +JMS X<br>+JIZ X<br>+JNZ X<br>+JPL X<br>+JMI X<br>+JCS X<br>+JCC X | n70 XXX<br>n72 XXX<br>n73 XXX<br>n74 XXX<br>n75 XXX<br>n76 XXX<br>n77 XXX            | Jump to Subroutine X  JMS if zero (Z=1)  " " not zero (Z=0)  " " positive (P=1)  " " negative (P=0)  " " C bit set (C=1)  " " C bit clear (C=0)                                                    |

Memory Reference Instruction Addressing Modes;

|                             | n | mnemonic |

|-----------------------------|---|----------|

| Direct (first 256 words)    | 0 | Х        |

| +Indirect (first 256 words) | 1 | @X       |

| +Direct relative            | 2 | + X      |

| +Indirect relative          | 3 | @+X      |

## TRIP

I was recently on a three day course at Salford University (An Introduction to Electrical Eng.) Part of the course involved a 'project' and I was lucky to be assigned to a project involving computing (analogue).

The project involved finding a suitable model to simulate a shunt wound d.c. motor.Our tutor helped us to find an equation (from first princip-

les) which related input voltage to speed.

We connected a motor up to a 'scope and observed that on switch-on the speed would slowly rise, overshoot, then settle down; on lower speeds the rise was slower and there was less overshoot. We therefore knew how our model ought to behave.

We were introduced to oue analogue computer, £1500 Vidac (Vidac 273 I think it was) and I will give brief details in case you are not familiar

with this machine;

The computing elements are fairly standard. integrators, multipliers and inverters with the addition of some logic elements; 'flip-flops', gates and, more important for an analogue machine, comparators (giving logic output which can be comparators (giving logic output which can be gated or stored in order to further control the system). There were 14 10 turn pots which could be used as dividers or for presetting voltages.

Output is fed to a 'scope or x-y plotter (with ramp for the x direction if required) or to a built-in 3½ digit DVM (which can also monitor pot leathing or to a built-ing or to a bui

settings etc.).

Also available were several push-buttons; Pot-set (self explanatory), Reset (resets the system), Initial Conditions (allows the initial conditions to be set up), Hold, Compute and Repeated Operation. The last allows continuous monitoring of the system whilst making adjustments (equivalent to on-line work with a digital !) and the sequence of operations is Compute, Reset, Initial Conditions etc. The speed can be set by an internal timer which has a 5/10/20 mSec/sec range, and which selects integration times (and x timebase if required).

With Compute the system computes continuously and needs to be reset manually if another operation

is required.

One good feature is that nearly every unit (integrators etc) has an overload warning light which comes on at about 1.3 units (on the DVM). In normal use the computer should only be operated between O and l units. (the DVM is calibrated to arbitrary 'machine' units as opposed to a particular standard voltage). This overload warning gives indication of which part of the 'circuit' has failed and in complex equations is very useful since overload of one part may not necessarily show at the output (although it may well have a detrimental effect) and troubleshooting may prove difficult.

We set up our equation and used a storage 'scope to plot our results. Unfortunately there were three parameters which we didn't know (relating to magnetic field strangth in the motor) and we found it was taking a long time to optimise these by 'guesswork'. Unfortunately also, the parameters were interlinked which meant if one was adjusted the other two had to be adjusted also. Finally we did, however, manage to get a reasonable approximation but we couldn't get any decent measurements from the system (we had hoped to find % overshoot etc).

In the 'Simulation' department there were quite a lot of analogue and digital machines. Some of the analogue machines were early valve types (huge chassis and PSU's) but one or two were more modern!

The digital machines were PDP8's (F I think) and "Lab 8" which I presume are similar to PDP8's. Some of the machines were linked to analogue machines for hybrid work. Facilities included a teletype, VDU's, disc and tape readers.

I managed to see (and play) a 'Space War' game,

in which two players have to control rockets and 'shoot' the other's rocket. The control system was specially built (no details since the unit was 'second-hand' and none were supplied) and featured left, right rotate, forward thrust and 'fire'. Output was on a standard VDU. I believe the program can be run on a PDP8 & VDU without the control (yoystick board) but I think data has to be entered via the switch register which might prove rather

P.D.Maddison

# DISPLAY

TELEWRITER \*

If anyone else is interested in building it I would be interested to know in case it is possible to get components cheaper for more than one

About the timing, this will have to be altered to suite UK TV standards won't it? The UHF modulator used in the PW Teletennis article could be used.

I'm also working on a unit for storing data on a cassette recorder. If anyone else is interested in these topics I should be grateful to hear from

I have an idea for using a calculator to work out operations and then produce the answers on a screen, not too difficult but very useful I forsee. The code for '+' could be tied into a calculator as could '-' and "=" etc and the output decoded from 7 segment to ASCII. The way I envisage doing this is to convert the 7 segment calculator display to BCD, stored in a shift register maybe, and then use codes 48 to 57 to enter digit data. An off the cuff way of testing all codes in the ROM could be to connect a binary counter + 64 to the inputs of the ASCII data entry points, the complete option set would then be seen. Also note that the BCD code for numbers preceded by two 'ones' gives the ASCII code - an easy way to get number devices to interface with the system. Mike Hewitt

25 Spring Lane, Sprotborough, Doncaster, Yorks

\* TV TYPEWRITER article, see V3, I1, p4 ed.

## SALE!

Hundreds of bits for sale; 30cps 8 track punch, 110 cps reader, transformers, veroboard, IC etc. J Florentin 44 Burleigh Rd., Hemel Hempstead, Herts HP2 4PP

# USA

On March 8, I got a PDP-11 in a trade for some other equipment, I also got a teletype. It was not in working order and I've spent all my spare time up to now bringing it up. It should be running by the end of the month. That would be great!

I also got a D-112 card set. The D-112 is a

copy of the PDP-8 made by Digital Computer Controlls. I hope to eventually bring it up alongside the PDP-11 for a dual processor system, but of course that's a dream and at least a year off.

I'd like to correspond with some of your members who'd be willing to just gab about computers. I'd be interested in learning a bit more about the amateur computing scene than you cover in your newsletter. I come across a lot of computer equipment here in the States and have increased my correspondence list to include 42 people around the country. I like to write letters and would be happy to further US/British relations any way I can. Gary Coleman

PO Box 7089 Arlington , Va , 22207

# STRUCTURE

STRUCTURED BASIC TRANSLATOR

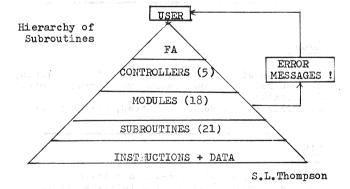

I have used the structured programming technique (though unbeknown for most of the time) in the design of a translator which enabled a BASIC subset to be used on a 4K 16 bit minicomputer.

The hierarchy of main program and subroutine levels I denoted as a Format Analyser, Controllers,

Modules and Subroutines.

The Format Analyser determines the user's input to be a statement, a command, a deletion, or a load of rubbish, viz;

120 LET A = B + C

RUN

100

\*!AZ99.,!?

The FA brings in one of five controllers which interpret the user's commands to RUN or LIST the program, to say good-BYE, to delete a statement or to store a statement (includes syntax analysis and encoding).

There were six statements in the BASIC subset; GOTO, IF, INPUT, LET, PRINT and END. Each of the 18 modules handles one type of statement in one of three modes - RUN, LIST and storage of a statement. In the event of user errors, a branch is made out of the module to give an error message. Control then returns to the user.

The Subroutines do the actual work of testing

and manipulating data.

A call and reply technique was used between Module and Subroutine. The Module places data in the accumulator, then calls the Subroutine. Now the given data may be out-of-range, the wrong type or OK. The Subroutine informs the Module of either state by 'replying' with a 'l' or a 'O' in the most significant bit of the accumulator.

The advantage of the structured programming technique here is that Controllers, Modules and Subroutines can be modified therebye altering the power of this BASIC subset e.g. the types of statement can be increased; each type can be altered in versatility eg PRINT could print variables and/or commentary, LET could perform simple addition and subtraction and/or more complex arithmetic functions.

# RAM CLUB

L. Elmer will be buying some 4K bit RAM, probably Motorola MCM 6605 L, and would be interested to hear from anyone interested in ordering with him near from anyone interested in ordering with him to raise the quantities and so lower the price. Cost is about £11 for one-off, dropping to around £7 if you buy more than 100. Ring him (weekends only) on 078 887 324 or write, but quickly, to 6 Atterbury Close, West Haddon, Northampton

# DATA

Intel (of 8080 fame) publish a huge catalogue of their memories/microcomputer components, at 15p each seems like a bargain. They are at Broadfield House, Between Towns Road, Cavendish, Oxford tel 771431. Their official distributors publish a list with prices, they are Rapid Recall and are at 9 Betterton St., London WC2H 9BS, tel 01-379-6741. In fact I got mine straight from Intel.

General Instrument Microelectronics publish a MOS Condensed Catalogue: ROM's, RAM's, PROM's, calculator chips, counter/drivers etc. They are at 57-61 Mortimer St., London WlN 7TD tel Ol-636-2022.

Sintel (53 Ashton St,Oxford) do a lot of MOS/CMOS chips-they publish a list/catalogue and will answer queries etc by phone (Oxford 43203). They seem very helpful to me...

Be warned that the cheap I/C supplier called DeMa (who advertise in Wireless World)wholive in the USA do not include 15% duty and 8% VAT in their prices!

A shortform catalogue of CMOS made by RCA (with connection data etc.) can be obtained from Celdis Ltd.,37/39 Loverock Rd, Reading RG3 1ED, tel Reading 582211.

Texas Instruments (Manton Lane, Bedford) publish an application note for the TMSO100NC series of calculator chips and a MOS/LSI specifications short form for design engineers.

P.S. Anyone around here who would be willing to answer my queries/help/drop in & chat ? Jeremy Wyatt The Rooks Nest, Charlbury, Oxon

# SALE!

I have for sale 3 blocks of 10 planes each of 48 x 52 bit core originally from 1301.

A cheap way of buying TTL is at radio rallies where you can buy a board of many devices, the individual price being a few pence each.

I am interested in connecting a small machine with teleprinters via amateur radio. Any one else? P Staton 847 Lincoln Rd., Peterborough PEL 3HG

# **BOOKLIST**

MICROPROGRAMMING G. Boulaye

£7.50 Macmillan

COMPUTER AIDED DESIGN OF ELECTRONIC CIRCUITS E.Wolfendale Illife

MINICOMPUTER SYSTEMS: ORGANISATION AND PROGRAMMING THE PDP-11 Prentice-Hall series in automatic computation. £9.80 1975

CYBERNETIC SERENDIPITY: THE COMPUTER & THE ARTS Ed. J Reichardt 1969 Frederick A Praeger

MacDONALD COMPUTER MONOGRAPHS:

9 USE OF FILES D.Judd

PROGRAM DEBUGGING A.Brown & W.Sampson

DIGITAL COMPUTER STRUCTURE & DESIGN R. Townsend 1975 £4.20 Newnes-Butterworths

MODULAR PROGRAMMING 1972 21.50 Newnes-Butterworths J.Maynard

```

January

INTEGER A,B

1:

2:

LOGICAL LEAP

DIMENSION A(7,6,12),B(504),MONTH(12),NAME(12),DAY(21),

3:

IDAY(28), LEAP(28)

4 :

EQUIVALENCE (A(1,1,1),B(1))

5:

DATA I.J.K.L.M.N.J1.J2.K1.K2/0.0.0.1.0.0.0.0.0.0/

6:

7:

DATA IDAY, LEAP/3,4,5,7,1,2,3,5<6,7,1,3,4,5,

6,1,2,3,4,6,7,1,2,4,5,6,7,2,

g:

FoFoToFoFoFoToFoFoFoToFoFoFo

9:

10:

T, F, F, F, T, F, F, F, T, F, F, F, T, F/

11:

DATA MONTH/31,28,31,30,31,30,31,30,31,30,31/

DATA NAME/'JAN', 'FEB', 'MAR', 'APR', 'MAY', 'JUN',

'JLY', 'AUG', 'SEP', 'OCT', 'NOV', 'DEC'/

12:

13:

DATA DAY/'SU','MO','TU','WE','TH','FR','SA',

14:

15:

'SU', 'MO', 'TU', 'WE', 'TH', 'FR', 'SA',

"SU', 'MO', 'TU', 'WE', 'TH', 'FR', 'SA'/

16:

17: 6000 FORMAT('1')

18: 6010 FORMAT(//)

19: 6020 FORMAT(34X,3(A4,29X),/,1X)

FORMAT(18X,3(5X,7(12,2X)),/)

20: 6030

21: 6040 FORMAT(18X,3(5X,7(A2,2X)),/)

22: 6050 FORMAT(/,97X, 'CALENDAR NUMBER ',12)

THIS

CALL YEARS

DO 5 II=1,28

23:

24:

DO 10 I=1,504

25:

26:

B(T)=100

PROGRAM

10 CONTINUE

27:

28:

KS=IDAY(II)

29:

PRINT 6000

30:

PRINT 6050,L

PRINT 6010

31:

PRINTS

OUT

Α

SET

32:

DO 40 K=1.12

NDAYS=MONTH(K)

33:

IF((K.EQ.2).AND.LEAP(II))NDAYS=NDAYS+1

34:

35:

DO 20 K1=1.NDAYS

CALENDARS.

B(K2)=K1

36:

K2=K2+1

37:

20 CONTINUE

38:

39:

30 K2=K2+7

IF(K2.LE.42*K)GO TO 30

40:

AND

40 CONTINUE

41:

DD 60 J1=1,10,3

J2=J1+2

42:

43:

IF(J1.NE.7)GD TO 41

44:

TABLE

45 .

PRINT 6000

46:

PRINT 6010

41 PRINT 6020, (NAME(J), J=J1, J2)

47:

48:

PRINT 6040, (DAY(M), M=1,21)

49:

DO 50 J=1.6

SHOWING

50:

PRINT 6030, ((A(I, J, K), I=1,7), K=J1, J2)

51:

50 CONTINUE

52:

PRINT 6010

53:

CONTINUE

WHICH ONE

L=L+1

TO

54:

CONTINUE

55:

56:

CALL EXIT

578

58:

SUBROUTINE YEARS

FOR

INTEGER*4 YEAR, N

59:

60: 1000 FORMAT(/,11X, 'FOR ',14,' USE CALENDAR NUMBER ',12)

FORMAT('+',47X,'FOR ',14,' USE CALENDAR NUMBER ',12)

FORMAT('+',83X,'FOR ',14,' USE CALENDAR NUMBER ',12)

61: 2000

62: 3000

YEARS

DATA YEAR, N. J/1755,10,0/

THE

63:

64:

DO 10 I=1,1245

J=J+1

65:

IF(YEAR . EQ . 1800) N=N-17

66:

IF (YEAR . EO . 1801) N=N-3

67:

IF(YEAR.E0.1900.OR.YEAR.E0.2300.OR.YEAR.E0.2700)N=N+5

68:

IF(YEAR • EQ • 1901 • OR • YEAR • EQ • 2301 • OR • YEAR • EQ • 2701) N=N+11

69:

IF(YEAR . EQ . 2100 . OR . YEAR . EQ . 2101

70:

* • OR • YEAR • EQ • 2200 • OR • YEAR • EQ • 2201

71:

*• OR • YEAR • EQ • 2500 • OR • YEAR • EQ • 2501

72:

1755

2999

73:

* • OR • YEAR • EQ • 2600 • OR • YEAR • EQ • 2601

74:

*• OR • YEAR • EQ • 2900 • OR • YEAR • EQ • 2901 ) N=N=6

IF(J.EQ.1)PRINT 1000, YEAR, N

75:

IF(J.EQ.2)PRINT 2000, YEAR, N

IF(J.EQ.3)PRINT 3000, YEAR, N

76:

77:

IF(J \cdot EQ \cdot 3)J = 0

78 :

79:

YEAR=YEAR+1

N=N+1

80:

IF(N.EQ.29)N=1

81:

82:

10 CONTINUE

83:

RETURN

84:

END

P. RUTHERFORD

```

So the Weeny-Bitter seems to have got off to a good start, next issue we should be able to start featuring the hardware design. Thanks to all those who are contributing to the design of both hard and soft ware aspects.

As you can see from the adjacent column we now have an ACC library, thanks to Mr. Doherty-Bullock. He has asked me to print a request for further contributions to the library - books, equipment

manuals, programs etc. So lay it on him folks.

While I'm still in an appealing mood, could I prevail upon someone to write us an article on Data Base techniques and applications ? Seems to be the latest 'thing', wish I knew something about it.

Membership has now reached 246, compared with last year's final figure of 281, and without any extra special recruiting drive we look like ending this year with around 260.At this figure and taking into account the £52 surplus from last year we should just about break even if inflation does not hot up again. Nevertheless, to be on the safe side we should try to recruit more. Jon Aslett has been contacting the electronic & computer magazines to try for some more free publicity but without success so far.

Inputs for the October issue by Oct 11 please.

m.lord

#### WHAT DO YOU THINK ?

A 'mind reading' system being developed at the Stanford Research Institute, California, monitors ECG signals and uses pattern recognition techniques to relate them to specific words. At present they are achieving around 50% accuracy with a 7 to 15 word vocabulary, not spectacular but its a

#### THE SCHOOL SYSTEM

A 64K English Electric System 4/30 with six tape drives, line printer & paper tape reader is now working at Imberhorne School, East Grinstead having been donated by the Standard and Chartered Bank last year. The school is now seeking a teletype with punch and, after the hot summer, some form of air conditioning.

# CODE CONVERSION

The following table gives the normal commercial code equivalents for the short alphanumeric codes sometimes found on 'surplus' IC's.

P.STATON

Generally suffix X means high speed 11  $\mathbf{z}$ ultra high speed

$\begin{array}{ccc} A & = & 7400 \\ AX & = & 74400 \end{array}$ 74H00 AZ = 74S00

#### 16 BIT MICROPROCESSOR

A 16 bit microprocessor chip, designed by General Instruments for Honywell, is now being made available for general sale in the UK. Called the 1600 CPU, it costs £121 (one off).

# LIBRARY LISTING

'Introduction to programming' (PDP-8) 'Small computer handbook ' SHOPLAN Dataskill production control system, leaflets

General Dataskill software sales literature, leaflets including details of operating systems

COBRA leaflet

11

11

IBM System 7 functional characteristics Extracts from Elektor, german electronics maga-zine describing hardware & instruction set considerations.

Index catalogue of Teletype KSR, ASR & RO 33 page printer parts.

Teletype ASR, KSR33 service manual, Vol I Literature about Ferranti's Argus machines. Ferranti press releases about past projects including traffic control & computer controlled manufacture.

Ferranti in offshore oil.

Ferranti - CEGB control centre.

- CP6 controllers.

- Packet switching - Computers in an information network.

- Details of PT7 programmable terminal.

- Description of support services.

- Dartford # 6 paper machine computer 11 11

control.

Univac 1106/1108 Algol reference manual. Univac 9400 software conventions reference manual. Univac OS/4 disc mapping program manual. Univac Uniscope 100 display terminal reference. Xerox Fortran IV-H language reference manual.

Fortran IV-H operations reference manual.

11 BASIC language reference manual.

11 APL reference manual.

11 CIRC-AC (circuit analysis) manual. Extended Fortran IV reference manual.

11 Volume initialisation reference manual. CP5 (Control Program 5) reference manual.

\*\* Universal time sharing OS

11 Sort/Merge reference manual.

TSL Telcomp 2 user manual. " Superstat user manual.

Olivetti TE 300 manual.

Xerox Peripheral Switching Equipment. CIRC-TR

Ħ CIRC-DC

Text formatting prog user guide.

In addition, Control Data have put their library at my disposal.

LIBRARIAN: F. DOHERTY-BULLOCK CRC Information Systems Ltd., 83 Clerkenwell Rd London ECLR 5HP

MEMBERSHIP of the ACC for the year 1 April 1975 to 31 March 1976 plus subscription to Vol 3 of the Newsletter costs £1 (50p for UK members who are aged 16 or under on 1 April 1975).

Vol 3 of the newsletter will consist of six issues, to be published at two month intervals.

AMATEUR COMPUTER CLUB NEWSLETTER

August 175 Vol 3 Iss 3

m.lord 7 Dordells, Basildon, Essex tel; 0268 411125 home 0268 3040 x 117 work